在现代电力电子和集成电路设计中,MOSFET(金属氧化物半导体场效应晶体管)因其开关速度快、驱动功率小等优点而广泛应用。对于高端(上桥臂)的N沟道MOSFET,其栅极电压必须高于源极电压才能有效导通。当源极电压随开关动作而浮动时,如何为栅极提供稳定可靠的驱动电压,成为了一个关键的设计挑战。自举电路(Bootstrap Circuit)作为一种简洁高效的解决方案,在各类开关电源、电机驱动器和逆变器等集成电路中扮演着核心角色。

一、自举电路的基本原理与构成

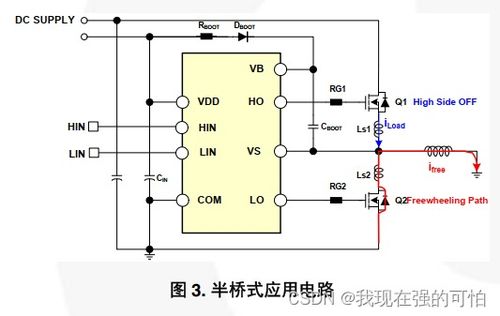

自举电路的核心思想是利用电容的储能与电压保持特性,为浮动的栅极驱动提供独立电源。其基本拓扑结构主要包括:

- 自举电容(Cboot):电路的能量存储核心。在低端MOSFET导通期间,电源Vcc通过自举二极管对Cboot充电,使其两端电压接近Vcc。

- 自举二极管(Dboot):实现单向能量传递,防止在高端MOSFET导通时,Cboot上的电荷向电源Vcc倒灌。

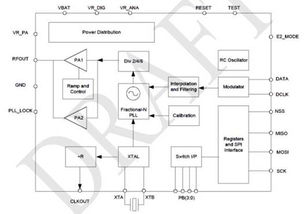

- 栅极驱动集成电路(Driver IC):通常集成有电平移位和驱动放大电路。其高端驱动部分的电源正端(VB)接自举电容正极,电源负端(VS)接高端MOSFET的源极(即开关节点)。

其工作过程为一个典型的“充-放”循环:

- 充电阶段:当低端MOSFET导通时,开关节点电压被拉低至接近地电位。此时,Vcc通过Dboot对Cboot充电,使

VB - VS ≈ Vcc。 - 驱动阶段:当需要导通高端MOSFET时,驱动IC利用Cboot上储存的电压作为其内部高端电路的电源,从而输出一个相对于其源极(VS)足够高的栅极驱动电压(通常为Vcc电平),确保高端MOSFET完全导通。

二、集成电路设计中的关键考量与优化

将自举电路集成到芯片内部或进行系统设计时,需要精心考量以下参数,以确保电路的可靠性和效率:

1. 自举电容的容值计算与选择

电容值必须足够大,以在高端MOSFET持续导通期间维持电压基本稳定,避免因栅极电荷注入和驱动电路静态功耗导致电压跌落过多。其最小值可估算为:

Cboot(min) > (Qg + Iboot * T_on) / ΔVboot

其中:

Qg为高端MOSFET的总栅极电荷。

Iboot为驱动IC高端通道的静态工作电流。

T_on为高端MOSFET的最大连续导通时间。

- ΔVboot 为允许的自举电容电压跌落值(通常设定为0.5V~1V)。

在集成电路设计中,通常会选择比计算值大2-5倍的电容,并优先选用低等效串联电阻(ESR)的陶瓷电容。

- 自举二极管的特性要求

- 反向恢复时间(trr):必须使用超快恢复或肖特基二极管,以最小化在充电瞬间由二极管反向恢复电荷引起的电流尖峰和损耗。

- 正向压降(Vf):较低的Vf可以减少对自举电容充电电压的损耗,确保

VB-VS足够高。在集成设计中,有时会用低压差的MOSFET开关来替代二极管,以进一步降低压降。

3. 最小导通时间与最大占空比限制

为了在每个开关周期内都能给自举电容有效补充能量,低端MOSFET必须保证一个最小的导通时间(Tminon),以便Vcc能够对Cboot完成再充电。这决定了电路能够支持的最大占空比(Dmax):

Dmax < 1 - (T<em>charge / T</em>sw)

其中Tcharge为充电所需时间,Tsw为开关周期。对于需要接近100%占空比的应用,需要采用电荷泵等更复杂的辅助电源方案。

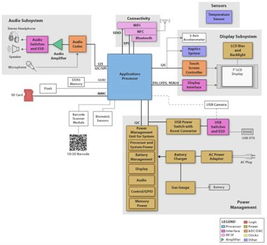

4. 高压工艺与电平移位

在集成电路内部,驱动芯片的高端部分通常需要集成高压电平移位电路,将来自低压控制逻辑的信号安全、准确地传递到以VS为参考点的高压侧。这涉及到高压隔离工艺(如BCD工艺)和抗噪声设计,是集成驱动芯片设计的核心难点之一。

- 噪声抑制与布局布线

- dV/dt噪声:开关节点(VS)的快速电压跳变会通过自举电容的寄生电容耦合到VB端,可能引起误触发。设计中需在VB和VS之间就近放置一个高频去耦小电容。

- 布局对称性:在芯片版图设计和PCB布局中,自举环路(Vcc→Dboot→Cboot→驱动IC高端→MOSFET源极)应尽可能短且面积小,以减小寄生电感和电磁干扰。

三、与展望

自举电路以其结构简单、成本低廉的优势,成为了驱动桥式电路中高端N-MOSFET的主流方案。在集成电路设计中,成功实现一个鲁棒的自举驱动方案,需要系统性地平衡电容尺寸、二极管性能、开关时序、工艺限制和噪声免疫等多重因素。

随着半导体工艺的进步,现代智能功率模块和集成驱动芯片已将自举二极管、充电控制乃至诊断保护功能(如欠压锁定)高度集成,极大地简化了外围电路并提升了系统可靠性。结合宽禁带半导体器件(如SiC、GaN MOSFET)更快的开关速度,对自举电路的充电速度、噪声抑制和集成度提出了更高要求,也将持续推动这一经典电路拓扑在设计与工艺上的创新。