在集成电路设计领域,数字集成电路测试系统是确保芯片功能正确性、性能可靠性与生产良率的关键环节。随着工艺节点不断缩小,芯片复杂度呈指数级增长,对测试系统的设计要求也日益提高。一个完整的数字集成电路测试系统设计,需融合电子工程、计算机科学与算法优化等多学科知识,其核心目标是在可控成本与时间内,高效检测出制造缺陷与设计瑕疵。

一、 测试系统的基本架构与组成

典型的数字集成电路测试系统主要由三大部分构成:

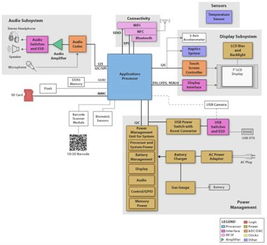

- 测试设备(ATE):作为系统的硬件核心,包括高精度电源、高带宽数字通道(用于施加测试向量和捕获响应)、时钟发生器、参数测量单元等。现代ATE需支持高速(GHz级)、多引脚(数千通道)并行测试,并具备良好的信号完整性与时序控制能力。

- 测试接口:包括负载板、探针卡或测试插座,负责将ATE的电气信号无损、可靠地连接到被测器件(DUT)。其设计需考虑阻抗匹配、寄生效应最小化以及散热问题。

- 测试软件与控制平台:这是系统的“大脑”,包括测试程序集(TPS)、测试向量生成与故障模拟工具、测试结果分析与诊断软件。它负责控制整个测试流程,生成并执行测试模式,分析响应数据,并生成测试报告。

二、 关键设计流程与考量

- 可测试性设计(DFT):这是芯片设计阶段就必须融入的理念。通过插入扫描链(Scan Chain)、内建自测试(BIST)电路、边界扫描(如JTAG)等结构,使芯片内部状态变得可控和可观测,从而极大地降低了生成高效测试向量的难度,并提高了故障覆盖率。

- 测试向量生成与优化:基于故障模型(如固定型故障、延迟故障),使用自动测试模式生成(ATPG)工具产生测试向量。设计挑战在于平衡故障覆盖率、测试向量集大小(影响测试时间)与测试功耗(避免芯片在测试中过热损坏)。

- 测试调度与成本控制:对于包含大量测试项(如DC参数测试、功能测试、高速AC测试、IDDQ测试)的芯片,需要优化测试顺序,并行测试策略,以最小化总测试时间,这是降低测试成本(通常占芯片总成本相当比例)的直接手段。

- 诊断与良率提升:测试系统不仅要说“好”或“坏”,更需具备诊断能力,能定位到具体的故障单元或互连线,为制造工艺改进和设计修订提供反馈,从而加速良率爬升过程。

三、 前沿趋势与挑战

当前,数字集成电路测试系统设计正面临以下趋势与挑战:

- 面向先进工艺与封装:针对3D IC、Chiplet等先进封装,测试系统需支持硅中介层测试、多芯片协同测试等新场景。

- 系统级测试(SLT)与在系统测试:随着SoC复杂性增加,单纯的结构测试已不足以保证系统级功能,SLT的重要性凸显,要求测试环境更贴近实际应用场景。

- 人工智能的应用:机器学习算法被用于优化测试向量、预测测试结果、进行智能诊断和良率分析,实现测试流程的智能化与自适应。

- 安全与可靠性测试:针对汽车电子、航空航天等高可靠应用,需引入更严苛的可靠性测试(如老化测试)以及针对硬件木马等安全威胁的检测机制。

结论

数字集成电路测试系统的设计是一个贯穿芯片设计、制造、封装全周期的系统工程。它不仅是产品质量的“守门员”,更是连接设计与制造、驱动工艺与设计迭代优化的关键反馈枢纽。未来的测试系统将朝着更高集成度、更高智能化、更紧密与设计流程融合的方向发展,以应对后摩尔时代日益严峻的芯片质量与可靠性挑战。优秀的设计需要在测试覆盖率、测试时间、硬件成本与诊断深度之间取得最佳平衡,从而为高性能、高可靠集成电路的产业化成功提供坚实保障。