在当今快速发展的半导体与集成电路(IC)设计领域,后端设计作为连接前端逻辑设计与物理实现的核心环节,面临着日益复杂的挑战。EETOP作为全球最大、最活跃的半导体、集成电路设计、嵌入式系统及电子电路工程师社区,汇聚了众多行业专家与开发者,其讨论区成为了探讨后端设计问题、分享经验与解决方案的重要平台。

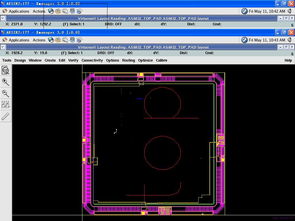

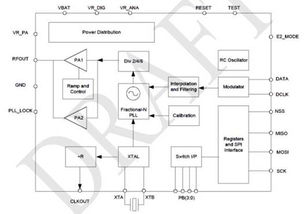

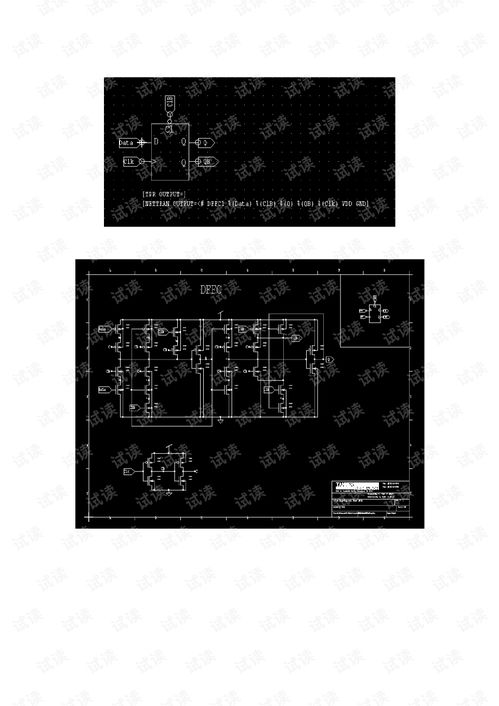

后端设计主要包括物理设计、时序分析、功耗优化、可制造性设计(DFM)等关键步骤。在深亚微米乃至纳米工艺下,设计者需应对信号完整性、时钟树综合、电源网络设计以及工艺变异带来的影响。例如,在先进工艺节点(如7nm、5nm)中,互连线延迟已超过门延迟成为主要瓶颈,这对布局布线工具和方法提出了更高要求。EETOP论坛中常见相关话题包括:如何利用工具(如Cadence Innovus、Synopsys ICC2)进行高效布局;低功耗设计技术如电源门控、多电压域的实现;以及针对特定应用(如AI芯片、物联网设备)的后端优化策略。

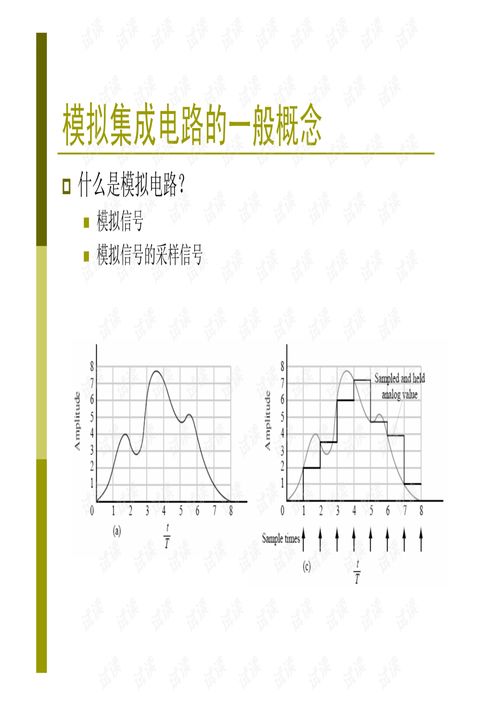

嵌入式系统设计与集成电路紧密相关,尤其在于系统级芯片(SoC)的开发中。后端设计需考虑处理器核、存储器、外设接口等模块的集成与协同,确保性能、面积和功耗的平衡。论坛中,工程师常讨论实时操作系统的硬件加速、内存层次结构对时序的影响,以及基于FPGA的原型验证与后端流程的结合。电子电路设计方面,模拟/混合信号IC的后端挑战尤为突出,如噪声隔离、衬底耦合效应的抑制,这些在EETOP的模拟电路板块常引发深入交流。

EETOP社区通过技术文章、项目经验分享及问题答疑,推动了后端设计知识的普及与创新。例如,有资深工程师分享利用机器学习辅助布局布线的案例,或探讨开源EDA工具在中小型设计中的应用前景。这些讨论不仅帮助解决具体问题,还促进了行业最佳实践的传播。

后端设计是半导体产业链中的关键一环,其复杂性要求工程师持续学习与协作。像EETOP这样的专业论坛,通过汇聚全球智慧,为应对技术挑战、推动集成电路与嵌入式设计发展提供了不可或缺的支持。随着新工艺和异构集成技术的演进,后端设计讨论将继续在社区中保持火热,引领行业前沿。