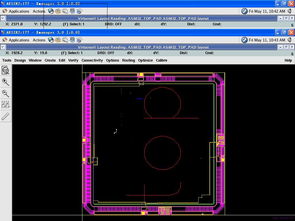

在掌握了反相器原理图设计与前仿真的基础上,本篇笔记将重点介绍集成电路物理实现的关键一步:版图设计与后仿真。

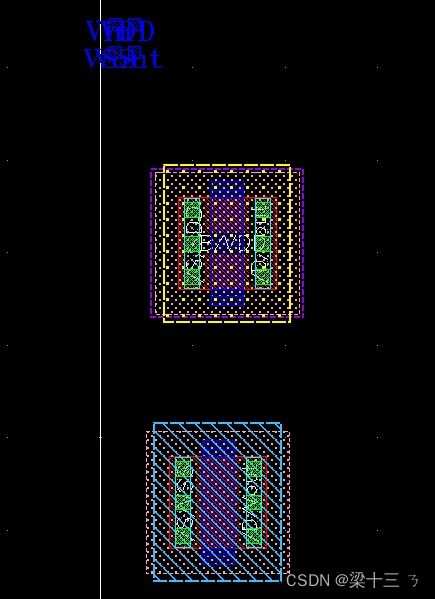

一、 反相器版图设计

版图是连接电路设计与芯片制造的桥梁,它将抽象的电路符号转换为制造光刻掩模所需的精确几何图形。

- 准备工作:

- 启动Virtuoso Layout Editor,调用已完成的CMOS反相器原理图单元。

- 设置正确的工艺设计套件技术文件,确保图层、设计规则与目标工艺完全匹配。

- 核心器件绘制:

- PMOS管:在N阱中绘制,需包含有源区、多晶硅栅、P+注入、接触孔及金属连线。栅极需与NMOS栅极相连,构成输入端。

- NMOS管:在P衬底(或P阱)中绘制,包含有源区、多晶硅栅、N+注入、接触孔及金属连线。

- 注意PMOS与NMOS的尺寸需严格匹配原理图中的宽长比。

- 连接与布线:

- 输出端:将PMOS的漏极与NMOS的漏极用金属线(如Metal1)连接,此连接点即为反相器的输出端。

- 电源与地:PMOS的源极连接至VDD电源线(通常用高层金属);NMOS的源极连接至VSS地线。

- 输入端:将两管的栅极用多晶硅或金属连接,构成输入端。

- 设计规则检查:

- 完成绘制后,必须运行DRC,检查版图是否符合工艺厂的所有最小间距、宽度、覆盖等物理规则。这是保证芯片可制造性的底线。

- 版图与原理图一致性检查:

- 运行LVS,将提取出的版图网表与原始原理图网表进行比对,确保两者在电气连接上完全一致,无短路、开路或器件匹配错误。

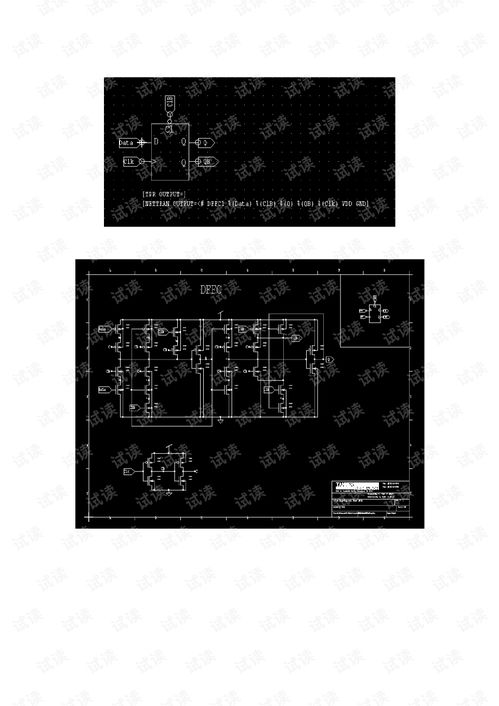

二、 寄生参数提取与后仿真

版图完成后,电路性能会受实际布线引入的寄生电阻、电容影响,必须通过后仿真进行验证。

- 寄生参数提取:

- 在通过DRC和LVS后,使用工具提取版图的寄生参数(PEX)。

- 提取模式通常选择“R+C”或“R+C+CC”,以获取寄生电阻、对地电容以及线间耦合电容。

- 后仿真设置:

- 生成一个包含所有寄生元件的“后提取”网表或视图。

- 在ADE仿真环境中,将待仿真的电路视图切换为此带寄生的视图。

- 关键性能对比分析:

- 瞬态特性:施加与“前仿真”相同的输入方波,观察输出波形。重点关注:

- 延时:通常由于寄生电容充电,上升/下降时间及传输延时会增加。

- 波形完整性:检查是否存在因寄生效应导致的过冲、回沟或振荡。

- 直流特性:再次仿真电压传输特性曲线,观察逻辑阈值、噪声容限是否有显著偏移。

- 动态功耗:由于对寄生电容充放电,动态功耗通常会高于前仿真结果。

- 迭代优化:

- 若后仿真结果不满足性能指标(如延时过大),需返回修改版图。常见优化手段包括:加宽关键信号线以减少电阻,增大驱动管尺寸以加快对寄生电容的充放电,或优化布线以减少耦合电容。

- 修改后必须重新进行DRC、LVS和提取,形成“设计-验证-优化”的闭环。

三、 与心得

从原理图到版图,是从理想世界走向物理现实的过程。反相器虽小,但其版图设计与后仿真流程完整地体现了集成电路物理设计的核心:

- 严谨性:DRC/LVS的通过是后续一切工作的基础,必须确保万无一失。

- 折衷艺术:版图设计是性能、面积、可靠性的多维折衷。例如,为了速度而增大晶体管或加宽金属线,必然会牺牲面积。

- 寄生意识:优秀的模拟设计者必须具备“寄生意识”,在版图阶段就预见到关键节点的寄生影响,并通过合理的布局布线(如对称性、屏蔽、匹配等)将其最小化。

至此,一个完整的反相器设计流程(原理图、前仿真、版图、后仿真)已走通。这为后续学习更复杂的电路模块,如差分对、运放、比较器等,奠定了坚实的实践基础。下一步,可以尝试设计一个带负载电容的环形振荡器,来综合应用和验证所学知识。