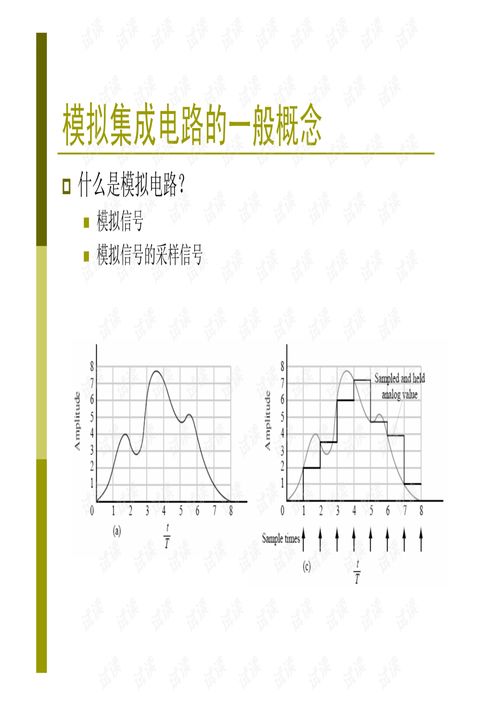

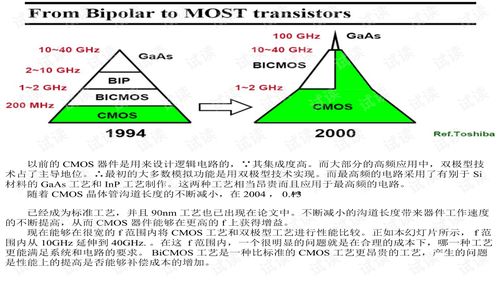

模拟BiCMOS(双极互补金属氧化物半导体)设计是集成电路领域一个关键且富有挑战性的分支,它巧妙结合了双极型晶体管(BJT)的高速度、高驱动能力和CMOS技术的低功耗、高集成度优势。对于从事高性能模拟、射频(RF)或混合信号芯片设计的工程师和学生而言,掌握其核心原理与设计流程至关重要。本文将探讨如何利用CSDN等平台的专业资源进行学习,并梳理集成电路设计中的关键考量。

一、模拟BiCMOS技术概述与设计挑战

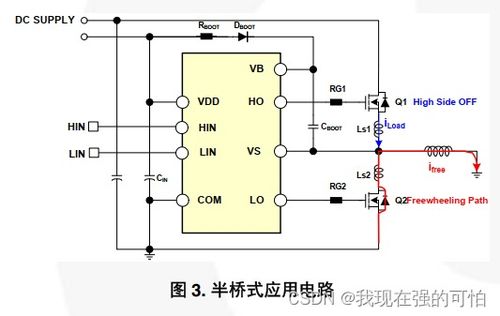

BiCMOS工艺允许在同一芯片上集成BJT和CMOS器件,使其非常适用于需要高速模拟前端(如放大器、比较器)与高密度数字逻辑或低功耗模块共存的场景,例如高速数据转换器、射频收发机、汽车电子及精密传感器接口。设计挑战也随之而来:工艺复杂度高导致成本增加;需要精心处理BJT与CMOS器件之间的匹配、隔离以及热效应;设计时必须综合考虑两种器件截然不同的特性(如BJT的跨导、CMOS的输入阻抗)以实现最优电路性能。

二、CSDN等平台的专业资源价值与获取指南

CSDN(中国开发者网络)作为国内知名的IT技术社区,汇集了大量工程师分享的实践经验、学习笔记、设计文档乃至工具脚本。对于模拟BiCMOS设计学习者,可以按以下方式高效利用:

- 精准搜索:使用关键词组合进行搜索,例如“模拟BiCMOS设计流程”、“BiCMOS工艺库使用”、“BJT与CMOS协同仿真”等。往往可以找到用户上传的PPT、PDF教程、项目或仿真代码。

- 甄别质量:优先选择点赞、收藏数高,且发布者具有相关行业背景认证的文档。关注那些系统阐述从器件物理、工艺入门到具体电路(如BiCMOS运算放大器、Bandgap电压基准源)设计的系列文章或资源。

- 实践结合:许多资源会涉及具体EDA工具(如Cadence Virtuoso, Synopsys HSpice)的操作指南。下载后,应结合官方手册和实际软件环境进行动手练习,完成从原理图输入、仿真到版图设计的全流程。

- 拓展渠道:除了CSDN,也应关注IEEE Xplore、arXiv等学术数据库获取前沿论文,以及厂商(如TSMC, GlobalFoundries)发布的工艺设计套件(PDK)文档和设计手册。

三、模拟BiCMOS集成电路设计核心流程

基于专业资源的学习,最终需落实到严谨的设计实践中。一个典型的模拟BiCMOS IC设计流程包括:

- 规格定义与架构设计:明确电路性能指标(增益、带宽、噪声、功耗等),并决定哪些功能块用BJT实现(如输入级、输出驱动),哪些用CMOS实现(如偏置电路、数字控制逻辑)。

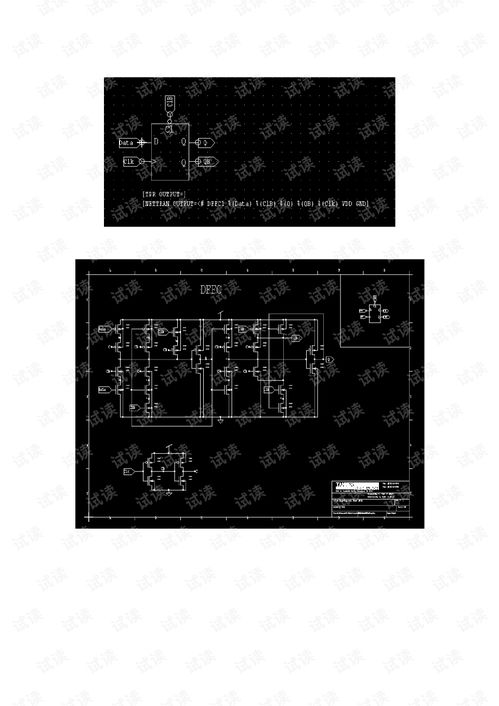

- 电路设计与仿真:在EDA环境中搭建电路原理图。关键步骤包括:

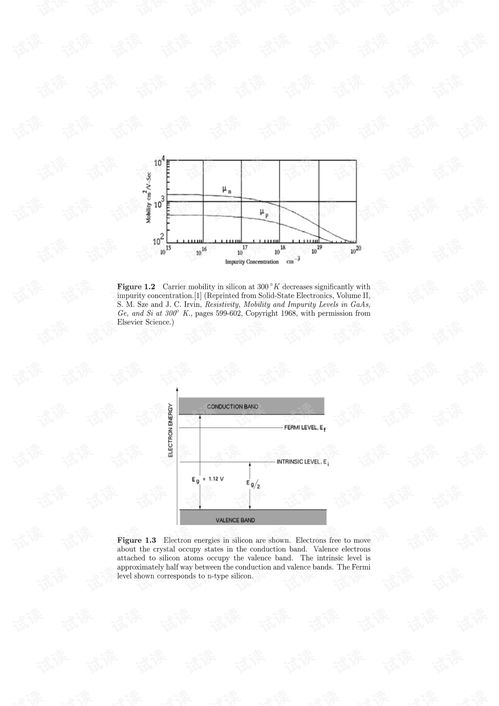

- 器件模型与选择:深刻理解PDK中提供的BJT(NPN/PNP)和CMOS(NMOS/PMOS)的SPICE模型参数,根据速度、增益、噪声等要求选择合适的器件尺寸和类型。

- 直流偏置设计:确保所有晶体管工作在合适的静态工作点,这是电路正常工作的基础。

- 交流与小信号分析:进行AC、噪声、瞬态仿真,优化增益、相位裕度、建立时间等动态性能。BiCMOS设计中需特别注意频率响应和稳定性的协同优化。

- 蒙特卡洛与角落仿真:分析工艺偏差、温度变化对电路性能的影响,确保设计的鲁棒性。

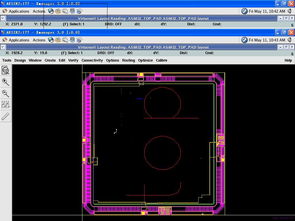

- 版图设计与验证:这是将电路图转化为物理掩模版的过程,在BiCMOS设计中尤为关键:

- 匹配与隔离:对精度要求高的器件(如差分对)采用共质心等匹配布局;利用深N阱、隔离环等技术有效隔离BJT与CMOS器件,防止闩锁效应和串扰。

- 寄生参数控制:精心规划走线,最小化互连电阻、电容,特别是高频路径上的寄生效应。

- 设计规则检查与版图比对:严格通过DRC确保符合工艺要求,并通过LVS确保版图与原理图一致。

- 后仿真与流片准备:提取版图寄生参数后进行后仿真,验证性能是否仍满足规格。最终生成GDSII文件交付晶圆厂流片。

四、学习建议与资源整合

对于初学者,建议遵循“理论-工具-实践”的路径:先通过经典教材(如Gray & Meyer的《模拟集成电路的分析与设计》)夯实器件和电路基础;再利用CSDN等平台的实操性资源熟悉EDA工具;最后通过一个完整的BiCMOS小项目(如一个两级运算放大器)将知识融会贯通。积极参与相关论坛的讨论,向经验丰富的同行请教,是解决实际设计中棘手问题的有效途径。

模拟BiCMOS设计是一门深度融合理论与工艺实践的学科。CSDN等社区提供的丰富资源是宝贵的学习起点和问题解决参考库,但最终的设计能力离不开对基本原理的深刻理解、严谨的工程实践以及对最新工艺技术的持续跟踪。通过系统性地学习与反复迭代设计,工程师能够驾驭这项技术,创造出满足高性能需求的复杂集成电路。